Bài giảng Kỹ thuật số (Phần 2)

I. Đại cương

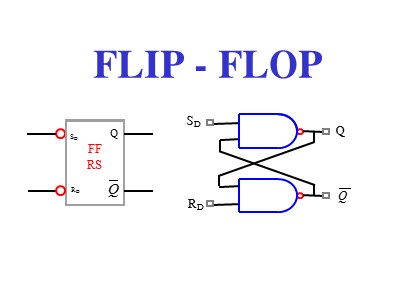

Flip Flop được mô tả bằng một ô vuông có nhiều ngõ vào chỉ có hai ngõ ra có tên là Q và có đặc tính liên hợp nhau nghĩa là Q = 1 thì = 0 hoặc ngược lại.

Ngõ ra có thể làm thay đổi hoặc không thay đổi trạng thái tuỳ thuộc vào ngõ vào và trạng thái của ngõ ra trước đó.

Bạn đang xem 20 trang mẫu của tài liệu "Bài giảng Kỹ thuật số (Phần 2)", để tải tài liệu gốc về máy hãy click vào nút Download ở trên

Tóm tắt nội dung tài liệu: Bài giảng Kỹ thuật số (Phần 2)

FLIP - FLOP S D R D FF RS Q Q S D R D I. Đại cương Flip Flop được mô tả bằng một ô vuông có nhiều ngõ vào chỉ có hai ngõ ra có tên là Q và có đặc tính liên hợp nhau nghĩa là Q = 1 thì = 0 hoặc ngược lại . Ngõ ra có thể làm thay đổi hoặc không thay đổi trạng thái tuỳ thuộc vào ngõ vào và trạng thái của ngõ ra trước đóù . Các trạng thái ngõ vào xác định trạng thái lý luận của Q và . Chỉ có hai ngõ ra liên hợp nhau khi : Q = = 0 hoặc Q= =1 ( thuộc tính cấm ) Những trạng thái ngõ vào làm cho hai ngõ ra giống nhau được gọi là trạng thái cấm và trên thực tế là không được phép xảy ra . II. Vận chuyển FF gồm 2 phần : Phần FF căn bản : gồm 2 mạch điện tử hoàn toàn giống nhau , mỗi mạch có một hay nhiều ngõ vào và chỉ có một ngõ ra Phần điều khiển : Phương pháp trực tiếp Phương pháp đồng bộ Tác động trực tiếp vào FF căn bản , khi bị kích thích mạnh thì Q bị ảnh hưởng ngay bất chấp ngõ điều khiển đồng bộ. Hai ngõ trực tiếp là S et (S D ) hay Preset (P D ) và Clear(C D ) hay Reset (R D ). K ích thích vào ngõ S D hay P D luôn luôn đưa Q lên 1 K ích thích vào ngõ C D hay R D luôn luôn đưa Q về 0. Điều khiển trực tiếp ( không đồng bộ ): Tác động vào mạch điều khiển động bộ K hi bị kích thích mạch chưa bị ảnh hưởng phải đợi đến khi có xung đồng bộ (Cp, T, Ck ) mạch mới bị ảnh hưởng. Điều khiển đồng bộ: III. Phương pháp kích thích Mạch phải được kích thích một cách hợp lý thì mới bị ảnh hưởng. Ta có 2 phương pháp kích thích bằng mức và bằng cạnh . Bằng mức: khi điện thế vượt qua mức ngưỡng nào đó làm kích thích mạ c h. Bằng cạnh: khi có sự thay đổi đột ngột từ thấp lên cao hay từ cao xuống thấp làm thay đổi mạch. Ta có 2 sự thay đổi từ thấp lên cao gọi là cạnh trước ( cạnh lên ) , từ cao xuống thấp gọi là cạnh sau ( cạnh xuống ) . Quy ước về ký hiệu : Mức 0 Mức 1 Cạnh lên Cạnh xuống 0 1 IV. Phân loại FF 1. FF RS Chỉ có ngõ điều khiển trực tiếp không có ngõ điều khiển đồng bộ S D R D FF RS Q Q S D R D Biến số Hàm số S D R D Q 0 0 1 1 0 1 0 1 cấm 1 0 Kh ông đổi Bảng trạng thái : 2. FF - JK FF-RS có điểm bất tiện , khi S và R ở mức cao thì ngõ ra bất ổn . S D R D Q CK Q J K J K CK Q 0 0 1 1 0 1 0 1 1 1 1 1 Q 0 (không đổi ) 0 1 ( đảo lại ) Trạng thái ngay trước khi đồng hồ lên cao Ngay khi có xung đồng hồ J K Q 0 S R Q 0 0 1 1 0 0 1 1 0 0 0 0 1 1 1 1 0 1 0 1 0 1 0 1 1 0 1 0 1 0 1 0 0 0 1 0 0 0 1 0 0 0 0 0 0 1 0 1 Q 0 Q 0 1 Q 0 Q 0 0 1 0 J K Q CK J K Q CK * FF nảy bằng cạnh lên * FF nảy bằng cạnh xuống J K CK Q 0 0 1 1 0 1 0 1 Q 0 (không đổi ) 0 1 ( đảo lại ) J K CK Q 0 0 1 1 0 1 0 1 Q 0 (không đổi ) 0 1 ( đảo lại ) 3. FF - D Khi nối ngõ vào của FF RS hoặc FF JK như hình vẽ , ta được FF chỉ có 1 ngõ vào D. J(S) K(R) Q CK D CK Q 0 1 0 1 0 1 D 1 1 0 0 CK Q 4. Chốt D Ở FF D khi thay ngõ vào đồng hồ bởi ngõ vào cho phép (Enable) tác động ở mức cao ta sẽ có mạch chốt D (D latch) Q D E(G) D E(G) Q E(G) D Q 1 1 0 0 1 x 0 1 Q 0 FF JK: 7470, 7472, 7473/LS73, 7476/LS76, 74107/LS107, 74LS112, 74LS114, FF D: 7474/LS74, 74174/LS174, 74175/LS175, 74LS364, 74LS374, 74LS573 Bài 3: MẠCH ĐĂNG KÝ DI CHUYỂN ( SHIFT REGISTER ) M ỗi flipflop có 2 trạng thái 0 hay 1 và ta có thể kích thích vào một trong hai trạng thái đó như ý muốn. Các ngõ ra chỉ thay đổi khi ta bắt buộc thay đổi. Ta nói flipflop có đặc tính ký ức. Nếu ta dùng nhiều flipflop ta có thể ghi vào chuỗi số nhị phân n bít với n là số FF và bit là đơn vị của FF. I. Đại cương Nhóm FF dùng vào công việc này để thành lập mạch đăng ký. Thường các FF không nằm cô lập mà được nối với nhau theo một kiểu cách nào đó , s ao cho có thể truyền dữ liệu cho nhau. Nhóm FF dùng vào việc điều khiển này thành lập mạch đăng ký di chuyển. 1 0 1 1 n bit II . Dữ liệu vào theo lối nối tiếp Ta dùng 4 FF dưới dạng FF - D được mắc như ở hình vẽ . D CLK Q CLR D CLK Q 9 CLR D CLK Q 9 CLR D CLK Q CLR Vào nối tiếp CK Ra nối tiếp Q A Q B Q C Q D Ra song song Đầu tiên ta có 4 FF bằng 0 ( nối clear xuống mass) ta tuần tự cho dữ liệu ở ngõ vào nối tiếp. Khi có một cạnh lên của xung C K dữ liệu đi vào trong mạch đăng ký di chuyển 1 bit , với dữ liệu n bit thì sau n xung CK dữ liệu nằm hoàn toàn trong mạch đăng ký di chuyển. Lúc đó ta có thể lấy ra theo lối song song bằng cách lấy các ngõ ra Q của các FF. Muốn lấy ra theo lối nối tiếp ta phải tiếp tục cho xung C K vào và sau n xung C K thì dữ liệu hoàn toàn ra khỏi mạch đăng ký di chuyển. DL vào CK Q A Q B Q C Q D 1 0 1 1 1 1 1 1 0 1 0 1 1 1 1 1 1 0 0 1 0 1 1 1 1 1 0 0 0 1 0 1 1 1 1 0 0 0 0 1 0 1 1 1 III . Dữ liệu vào theo lối song song & 74LS00 1 74LS04 J CK K Pr Cl QA FF J-K & & 1 Pr Cl QB FF J-K & & 1 QC FF J-K & A = 1 B = 0 C = 1 Q A Q B Q C Song song Điều khiển nhận vào Clock Ra nối tiếp Vào song song K CK CK J J K Pr Cl Muốn cho dữ liệu vào theo lối song song , ta phải đặt sẵn dữ liệu tại các ngõ A, B, C . K hi ngõ điều khiển nhận vào lên 1 ta thấy : Nếu A = 1 nên Q A = 1. Nếu B = 0 nên Q B = 0. Ta nói dữ liệu từ ngõ vào được đưa đến ngõ ra khi ngõ điều khiển nhận vào lên 1. Ngõ đồng hồ CK không có tác dụng khi nạp song song. Muốn ngõ ra theo lối nối tiếp , ta lấy ở ngõ cuối cùng. Muốn mạch dịch trái , ta phải nối các đường hồi tiếp Q C về ngõ vào B, Q B về ngõ vào A và ngõ ra Q A chính là ngõ ra nối tiếp , ngõ vào nối tiếp chính là ngõ vào C. Khi lấy ra theo nối tiếp thì dữ liệu sẽ bị mất đi . M uốn dữ liệu không bị mất , ta nối đường hồi tiếp từ ngõ ra cuối cùng trở về ngõ vào đầu . Ta cần thêm 1 số c ổng logic để thiết kế dữ liệu vào theo lối nối tiếp, thiết kế dữ liệu vào và ra theo lối song song, hoặc dữ liệu ra nối tiếp và nối đường hồi tiếp để mạch chạy tuần hoàn. Ra nối tiếp MẠCH ĐKDC Ra song song Vào nối tiếp ĐK ĐK = 0: vào nối tiếp ĐK = 1: hồi tiếp ( chạy tuần hoàn ), 74164 Mạch dịch trái : S CK R QA S CK QB QA QB 74LS04 1 R Vào nối tiếp Ra nối tiếp CK Mạch dịch phải : Ra nối tiếp S CK R QA S CK QB QA QB 1 74LS04 R CK Vào nối tiếp Thí dụ : 7494 : 4 bit, vào // hay nối tiếp – ra nối tiếp 7495 : 4 bit, vào // hay nối tiếp – ra // hay dịch phải trái . 74164: 8 bit, vào // - ra nối tiếp 74194: 4 bit, vào // hay nối tiếp – ra // , nạp đồng bộ , dịch phải/trái . IV. ỨNG DỤNG Lưu trữ và dịch chuyển dữ liệu . Tạo ký tự hay tạo các dạng điều khiển . Chuyển đổi dữ liệu từ nối tiếp ra song song hoặc ngược lại .

File đính kèm:

bai_giang_ky_thuat_so_phan_2.ppt

bai_giang_ky_thuat_so_phan_2.ppt